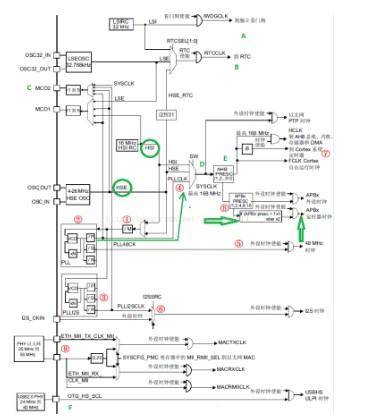

1.首先注意的的是图中画绿色圈圈的两个,HSE和HSI分别表示外部时钟和内部时钟,其中HSE 是是高速外部时钟,可接石英/陶瓷谐振器,或者接外部时钟源,HSE 也可以直接做为系统时钟或者 PLL 输入(从红圈4处可以看出),频率范围为 4MHz~26MHz。STM32默认为25Mhz,像原子的板子就是8Mhz的,所以移植时一定要格外注意。

2.注意红圈2代表的部分,这里是主锁相环倍频输出,用于产生系统需要的高速时钟信号,如图绿色箭头所示(STM32还有一个副锁相环,如红圈3)

主 PLL 时钟的时钟源要先经过一个分频系数为 M 的分频器,然后经过倍频系数为 N 的倍频器出来之后的时候还需要经过一个分频系数为 P(第一个输出 PLLP)或者 Q(第二个输出 PLLQ)的分频器分频之后,最后才生成最终的主 PLL 时钟。例如我们的外部晶振选择 8MHz。同时我们设置相应的分频器 M=8,倍频器倍频系数 N=336,分频器分频系数 P=2,那么主 PLL 生成的第一个输出高速时钟 PLLP 为:PLL=8MHz * N/ (M*P)=8MHz* 336 /(8*2) = 168MHz(来源:正点原子)

3.区分APB1和APB2

如红圈8表示的位置,STM32F4 很多外设的时钟来源,即两个总线桥: APB1 和 APB2,其中 APB1是低速总线(最高 42Mhz),APB2 是高速总线(最高 84Mhz)。另外定时器部分,如果所在总线( APB1/APB2)的分频系数为 1,那么就不倍频,如果不为 1(比如 2/4/8/16),那么就会 2 倍频( Fabpx*2)后,作为定时器时钟输入。

简单点说,举个APB1的例子,系统时钟是168Mhz,APB1分频系数为4(system_stm32f4xx.c配置),则APB1速度为42Mhz,但是挂靠在在该总线上的定时器3,由于分频系数4而不是1,因此定时器输入频率为42Mhz x 2 =84 Mhz,具体详见这篇文章点击打开链接

4.AHB总线频率

见图

上一篇:如何采用SysTick来做定时器

下一篇:STM32单片机DAC输出电压的功能解析

- 热门资源推荐

- 热门放大器推荐

- LDK120M12R 1.2V低压降稳压器典型应用(可调版)电路

- EVB-UTC2000-DFP、EVK-UTC2000 评估套件基于 UTC2000 USB 3.0/2.0 Type-A,即插即用 Type-C DFP

- LTC3219 演示板、250mA 通用九通道 LED 驱动器

- DC919A-D,LTC2204 CMOS 输出演示板,直流输入,40Msps 16 位 ADC,DC

- AD8618ARZ-REEL 二阶低通滤波器运算放大器的典型应用电路

- 使用 NXP Semiconductors 的 PCA9511A 的参考设计

- LT3091MPDE 恒流恒压实验室电源的典型应用

- ADR392B 4.096 Vout 微功率、低噪声精密电压基准的典型应用

- LT3470HDDB 5V 降压转换器的典型应用电路

- 使用 Diodes Incorporated 的 AZ7042ZTR-E1 的参考设计

非常经典的关于LLC的杨波博士论文

非常经典的关于LLC的杨波博士论文 MB47082PS

MB47082PS

7662CPA

7662CPA

京公网安备 11010802033920号

京公网安备 11010802033920号