如果用一句话总结半导体的发展史,可以说是不断在无法想象的微观尺度上“雕花”。时间回到四五十年前,那时候复杂SoC或芯片只有20万个晶体管,时至今日,市面很多AI芯片的晶体管数量达到了2000亿个。换句话说,四五十年以来,芯片上的元件数量翻了100万倍。更恐怖的是,芯片正在朝向2030年达到万亿晶体管的目标进发。

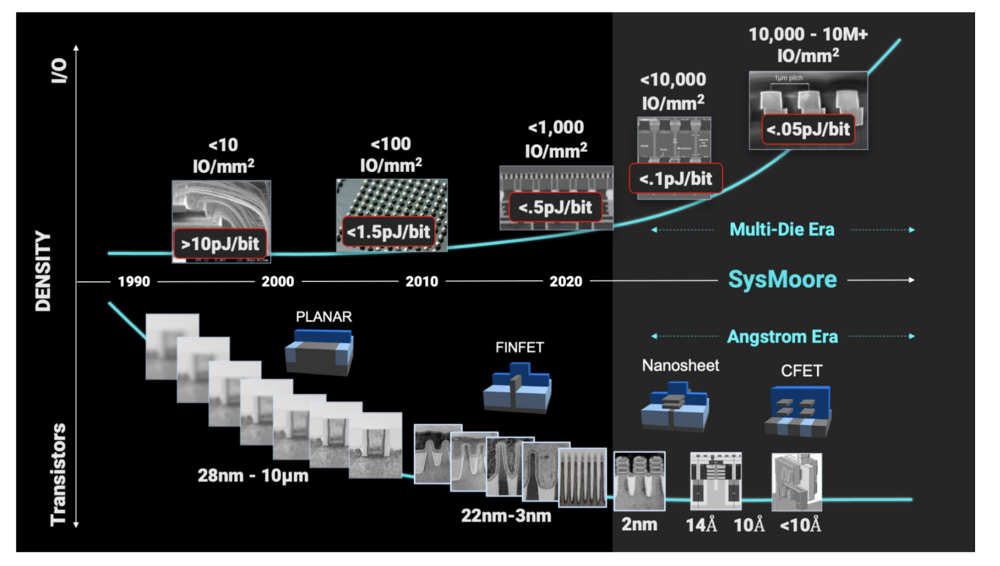

人类之所以努力,是因为半导体行业经历了PC、手机这样的市场爆发,需要让芯片在同样面积上,盛下更多晶体管。反观当下,AI无疑是改变世界的一个新的转折点,一个万物智能时代正在到来。随着摩尔定律逐渐放缓,我们正在无限逼近芯片的物理极限,这种情况下,就不能光盯着制程去升级芯片性能,片上异构集成、先进封装、Chiplet(小芯片)这些都会是芯片提升性能的关键。

芯片对于PPA的追求是无止境的,为了继续延续摩尔定律,人们给出的答案是Chiplet(小芯片),也就是Multi-Die芯片系统。所谓Multi-Die指的是被细分成多个功能电路模块,这些电路块被称为小裸片(small Die)或者小芯片(Chiplet)。这些小芯片通常采用不同的工艺节点制造,并被集成到单个封装中,最终满足PPA的目标。换句话说,Multi-Die(多芯片系统)就是目前快速提升芯片性能的秘密。最近一段时间内,Multi-Die解决方案开始崭露头角,为芯片功能扩展提供了一条制造良率较高的路径。

日前,新思科技总裁兼首席执行官Sassin Ghazi便围绕着“万物智能”这一主题进行了演讲,同时推出业界首个完整用于Multi-Die设计的40G UCIe IP全面解决方案。

根据Sassin Ghazi的介绍,新思科技能够在万物智能时代,为Multi-Die给出三方面的解决方案——一是广泛IP核组合,二是EDA平台,三是高级封装,也就是先进的Multi-Die解决方案。

IP核组合:率先推出40G UCIe IP

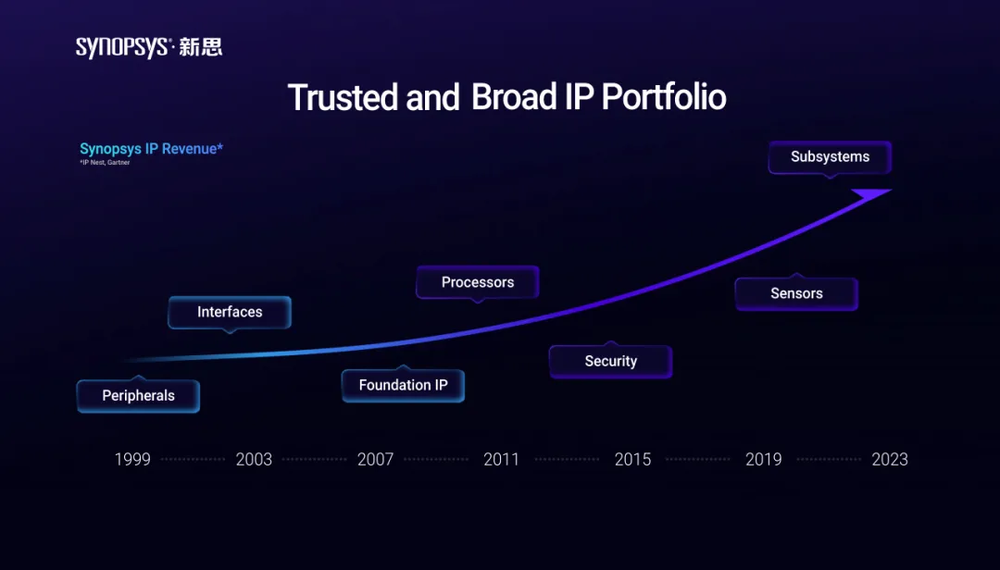

根据Sassin Ghazi的介绍,新思科技从事IP业务已有近26年,最初主要提供Design Compiler所需的小模块,比如加法器和乘法器,使客户在综合设计时无需从头开发。随后,新思的IP库逐渐扩展到外设IP、接口IP、基础IP、安全IP、处理器IP,甚至到子系统IP。例如,一个包含控制器、PHY及相关逻辑的子系统IP,这是芯片的重要组成部分,但客户通常不愿投入过多资源设计这部分,因为其复杂性较高。

大多数客户可以自己研发相似功能的IP,但关键问题在于:这是否是资源的最佳利用?是否有助于实现产品差异化?如果答案是否定的,那么客户可以考虑采用新思科技广泛的IP产品组合,涵盖基础IP、安全IP、接口IP、处理器IP等多种类型。

作为全球领先的接口IP企业,新思科技致力于提供广泛的IP核组合,并为此感到自豪。

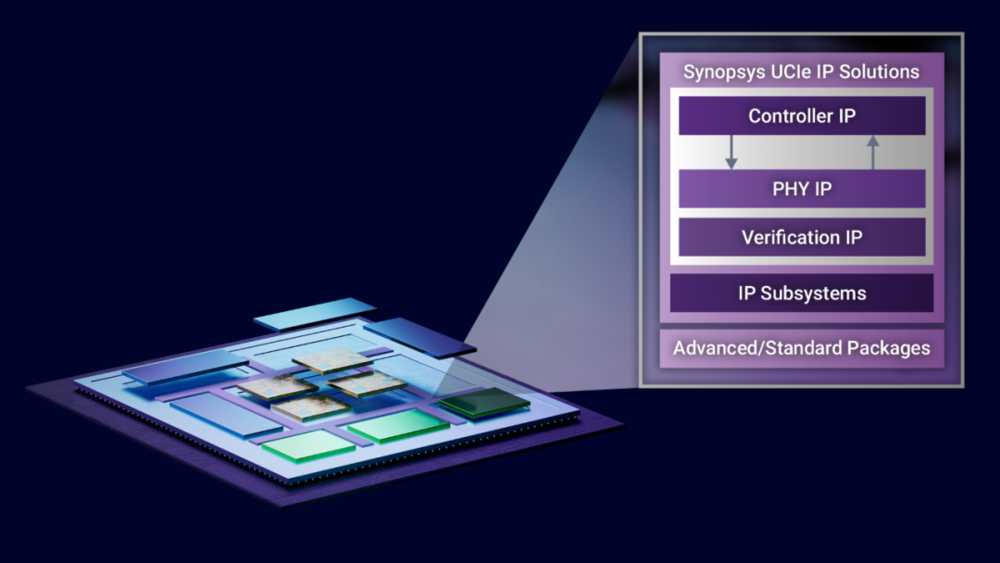

在Multi-Die方面,新思率先推出用于Multi-Die设计的40G UCIe IP。Sassin Ghazi表示,这是一次非常大的突破,比如从单芯片设计转到多芯片设计系统,一定要避免带宽损失,避免功耗和面积增加,利用40G UCIe IP能够实现比UCIe规范高25%的带宽,它还集成了许多SI监控器,有助于提高芯片生命周期可靠性。

此外,40G UCIe IP解决方案比不仅能够提高带宽,新思科技40G UCIe IP提供了测试和芯片生命周期管理(SLM)功能,还集成了能够提高可靠性的先进控制器和传感器。

为什么要先推出这样一个UCIe的IP?想象一下,Multi-Die系统的可能晶粒可能包含很多不同的供应商,假设每个芯片都采用不同的工艺技术,例如 7nm 和 3nm,如果想让这两个芯片能够无缝地相互通信,并支持行业标准协议,例如PCIe和CXL等,设计中每个Die都会让系统加大延迟。UCIe就能够克服这个障碍,它能够确保互操作性并降低延迟,并且支持通过冗余通道进行维修。

EDA平台:超融合、端到端的平台

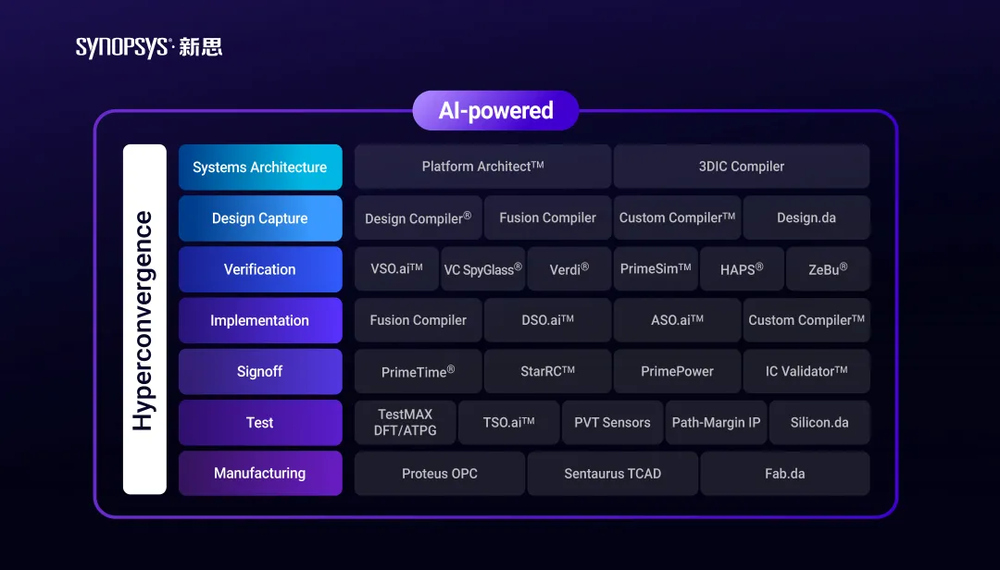

Sassin Ghazi介绍,在EDA平台方面,新思科技具有显著优势,能够打造真正的端到端的EDA平台。这一平台涵盖从TCAD晶体管器件级建模和仿真工具,到Platform Architect系统级设计工具,提供了一个全面的解决方案,涵盖系统架构、设计捕获、签核、测试和制造等各个环节。

值得一提的是,七年以前,新思便对EDA平台进行了超融合,也就是新思推出的Fusion Design平台。它将芯片时序、功耗和可靠性等复杂特性进行整体综合考虑,使其能够在流程的每个步骤中研究,哪些引擎是可以共用的,以便为客户提供可预测性,助力其确定该流程的最佳PPA。

此外,新思还引领了AI在EDA行业的普及,2017年便开始研究使用AI缩短设计时间,更快交付芯片,并在实现更优PPA方面取得很好的进展,台积电便是典型案例之一。

2020年,新思推出业界首个AI驱动型芯片设计解决方案DSO.ai;到2023年新思又发布业界首个全栈式AI驱动型EDA整体解决方案Synopsys.ai。作为全球硬核技术的领导者,新思科技率先布局并不断将AI融入到EDA技术中,引领AI+EDA设计新范式。

截至目前,Synopsys.ai已搭载设计优化解决方案(DSO.ai™)、验证解决方案(VSO.ai™)和测试解决方案(TSO.ai™)、模拟解决方案、AI驱动型数据分析整体解决方案DesignDash、生成式AI助手Synopsys.ai Copilot以及用于3D设计空间优化的3DSO.ai,并还在持续进行优化,以底层技术之力不断推动AI技术的发展。

在Multi-Die方面,新思的Platform Architect可以针对裸片芯片进行建模,展开仿真和分析,并在RTL可用之前,再次对不同裸片芯片的选择进行建模、仿真、分析,助力Multi-Die快速落地。

要成功采用Multi-Die异构集成,关键在于克服3大挑战,一是多方位尺度,二是多方位物理,三是多方位组织。通过新思科技的PrimeTime、Fusion Compiler和3DIC Compiler与Ansys的RedHawk-SC等产品来帮助开发者应对这些挑战。

Multi-Die解决方案:芯片封装的进阶之路

Multi-Die系统级封装(SiP)的优势很多,包括可开发具有更多功能的产品可通过更换裸片快速开发出多个SKU可使用经过验证的裸片,减少开发风险与使用两个独立的芯片相比,multi-Die吞吐量更高,系统功耗更低可优化系统外形尺寸,降低系统成本与使用两个独立的芯片相比,裸片间的低延迟可以提高系统性能。

如今,新思则跟踪了一百多种Multi-Die设计,其中既有硬件/软件数字孪生方法、Multi-Die 连接IP方法,也有AI驱动的芯片设计方法。

为什么新思要大力发展Multi-Die?通过科技与经济的视角,新思持续将技术突破与经济发展的机遇进行挂钩。过去数十年来,晶体管的尺寸按照摩尔定律不断微缩,而近年来Multi-Die连接方面的进展同样令人惊叹。芯片连接密度不断增加,而每比特的开关能耗却在不断降低,随着埃米级晶体管与Multi-Die硅基板交汇融合,经典的摩尔定律已将接力棒传递给了SysMoore。

Sassin Ghazi曾表示,在2030年之前,高端Multi-Die系统的涓涓细流将变成滔滔洪流,覆盖每个适用市场。Multi-Die系统是新思科技和整个行业非常关心的一个主题,未来几年,随着新功能的发展,这方面的消息会越来越多。对于新思科技而言,如今95%以上的先进芯片都采用新思科技的技术制造。现在,新思正在跟踪100多种Multi-Die系统设计,该数目在过去六个月增长了约20%。透过这一增长,可以看出Multi-Die系统设计方向正在迅速走向成熟。

当技术、厂商、开发者一切都融合在一起

把EDA、IP、Multi-Die有机集合在一起的关键,就是AI。“我们正处在AI的关键转折点,这是一次重大的转型,AI或将参与到公司内的所有工作流程中,不断改变我们参与、运营、开发产品以及与生态系统互动的方式。”Sassin Ghazi如是说。

AI对于简化、支持和加快客户研发以及提高开发效率不可或缺。在芯片和先进封装方面,将这些Multi-Die以及Multi-Chiplet分解并集成到先进封装中,一定是未来在芯片系统中实现更多复杂功能的关键。在考虑系统设计,也就是芯片与系统之间的桥梁时,需要考虑芯片生命周期管理。因为系统一旦投入实际使用,就需要确保其可靠性,并保证现场应用的反馈能够回到驱动系统的芯片中,这两点非常重要。

想要更好地把技术融合,与厂商的写协作必不可少。新思科技中国区副总经理姚尧表示,今年,新思携手英伟达深化合作,将新思科技领先的AI驱动型电子设计自动化(EDA)全套技术栈部署于英伟Grace Hopper超级芯片平台,在芯片设计、验证、仿真及制造各环节实现最高15倍的效能提升。

需要融合的不只是厂商,还有开发者。新思科技全球资深副总裁、新思中国董事长兼总裁葛群先生表示,新思科技开发者大会为广大开发者提供共同交流全球科技发展、探索生态合作范式的平台,激发不同行业的开发者们一起参与到万物智能时代的创新浪潮中。新思将加速技术创新步伐,与千行百业“在一起”,与开发者“在一起”,打造从芯片到系统的超融合创新平台,为全球科技发展提供源源不断的动力。

他强调,2019年新思把Synopsys User Group变成China Developer Conference。对此,他的思考是,当大家拿到一个用户手册的时候,这本手册会告诉我们工具怎么使用。但是,世界的演进依靠的是众多的创新者、开发者们,因为大家的创新思维已经超越了工具和用户手册本身所界定的技术范围。因此,这个平台的发展离不开在座所有想要改变世界的开发者。

上一篇:本土自研再上新!安谋科技发布首款“玲珑”DPU和新一代VPU

下一篇:西门子EDA新任CEO中国首次演讲,说了这几件事

推荐阅读最新更新时间:2026-03-24 12:26

- REF196 精密微功率、低压差堆叠电压基准的典型应用电路

- LTC4367IMS8 用于滞后调节的过压电源控制器的典型应用

- CLRC663非接触式读写器IC的典型应用

- 使用 ON Semiconductor 的 CS-5621 的参考设计

- RSO-0515S 15V、67mA输出DC/DC转换器典型应用电路

- NCP51200 3 Amp VTT 终端稳压器 DDR1、DDR2、DDR3、LPDDR3、DDR4 的典型应用

- LR645大电流SMPS启动电路典型应用

- ADR420 可编程电流源的典型应用

- DC417B,使用 LT1806CS8 多尺寸单运算放大器原型的演示板

- DM300019,用于评估 dsPIC30F 和 dsPIC33F MCU 系列器件的 dsPICDEM 入门开发板

API调用模型小助手-桌面版

API调用模型小助手-桌面版 深度学习

深度学习 英集芯IP2366-140W-PD充电芯片DEMO资料

英集芯IP2366-140W-PD充电芯片DEMO资料 现代雷达系统的信号设计

现代雷达系统的信号设计

BFR340T

BFR340T

京公网安备 11010802033920号

京公网安备 11010802033920号